Vol.7 技術情報

水晶発振回路の回路マッチングとは⑥【回路マッチングの手法…抵抗挿入法】

回路マッチングの手法

九州電通で行っているマッチングの方法は「抵抗挿入法」と言いますが、この章では手順を簡単に説明しておきます。

なお、回路マッチングを始めるまえに回路に搭載する水晶振動子の測定データを明確にしておく必要があります。

その項目は下記のとおりです。

(1)指定負荷容量で測定した周波数(fL)

(2)ESRの測定値と規格値

(3)並列容量C0の測定値

(4)負荷容量

● 負性抵抗(-R)を求める

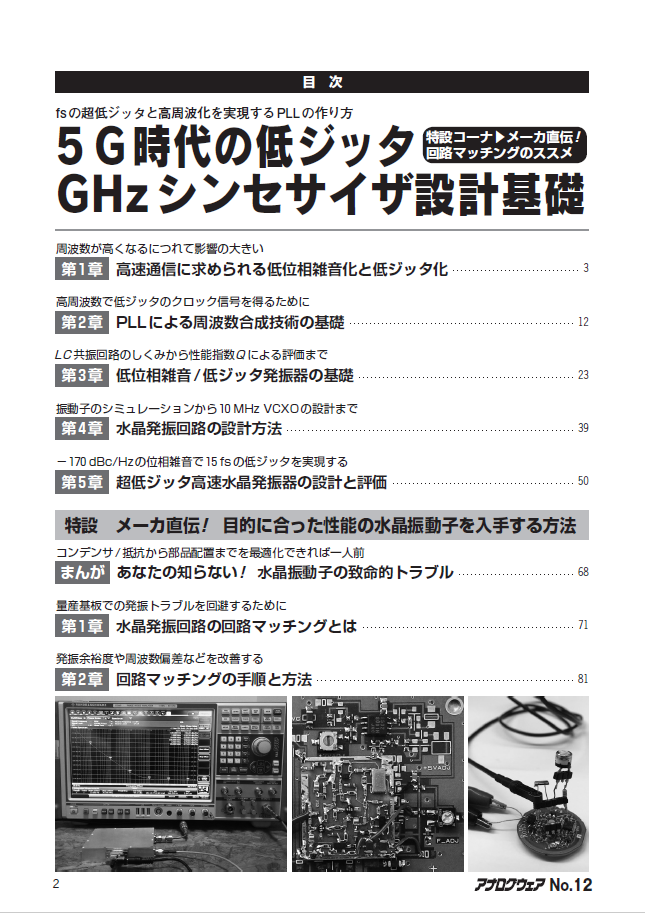

①振動子を回路から取り外し、図5 のように可変抵抗RVと直列に接続したうえで回路に接続する

②RVを最大にして発振を止めておく

③RVを徐々に下げていって発振を開始する段階の抵抗値を測定する

このポイントが発振しようとするプラスのパワーと、発振を阻止しようとするマイナスのパワーがバランスするポイントです。

RVを0から徐々に上げていってもほぼ同じです。

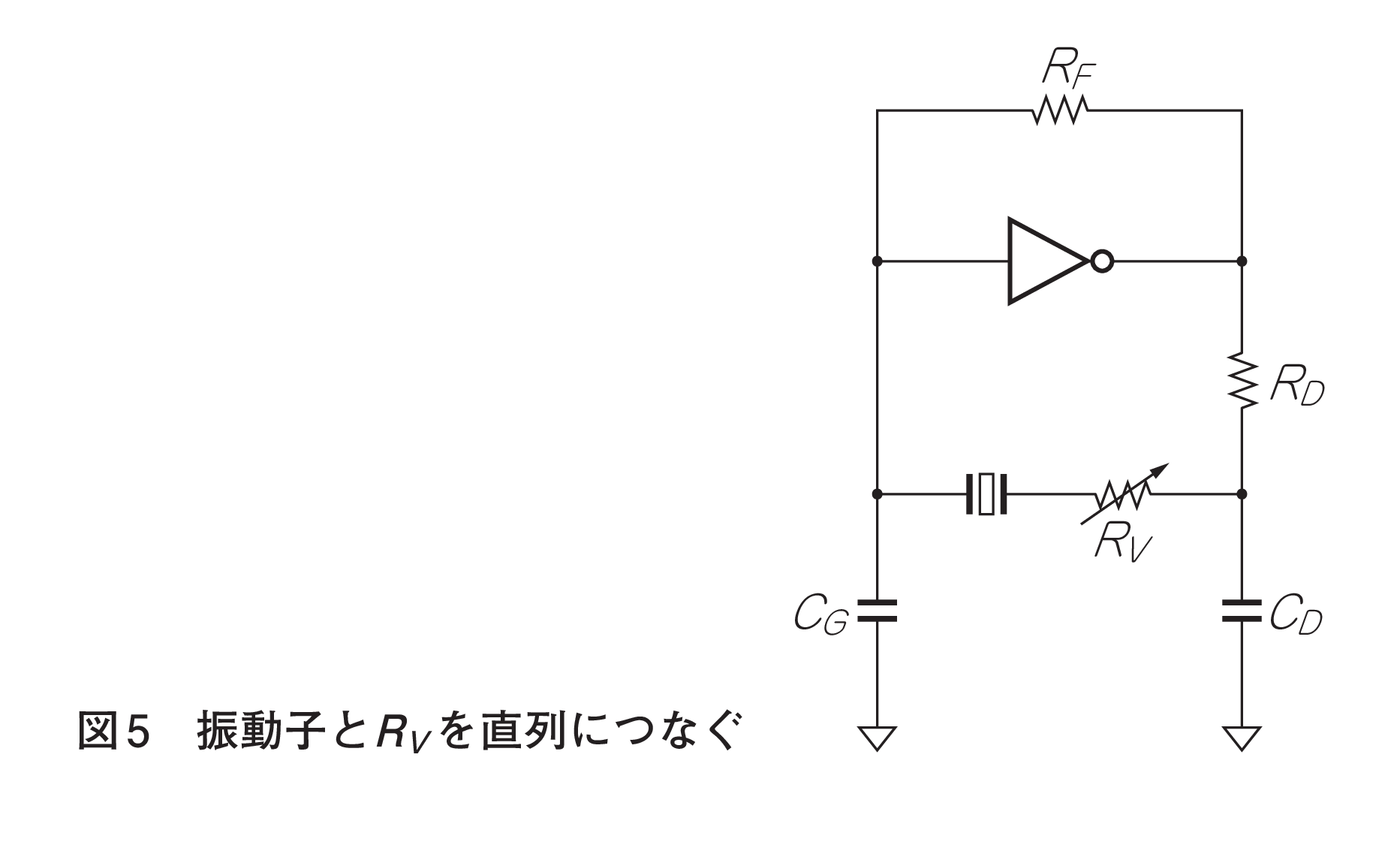

④RE(負荷時等価抵抗)を式(2)で求める

ここで、RSは上記(2)の当該サンプルのESR測定値、C0は並列容量値、CLは負荷容量値です。

⑤-R(負性抵抗)を式(4)で求める

これらを図示すると図6のようになります。

● 発振余裕度を求める

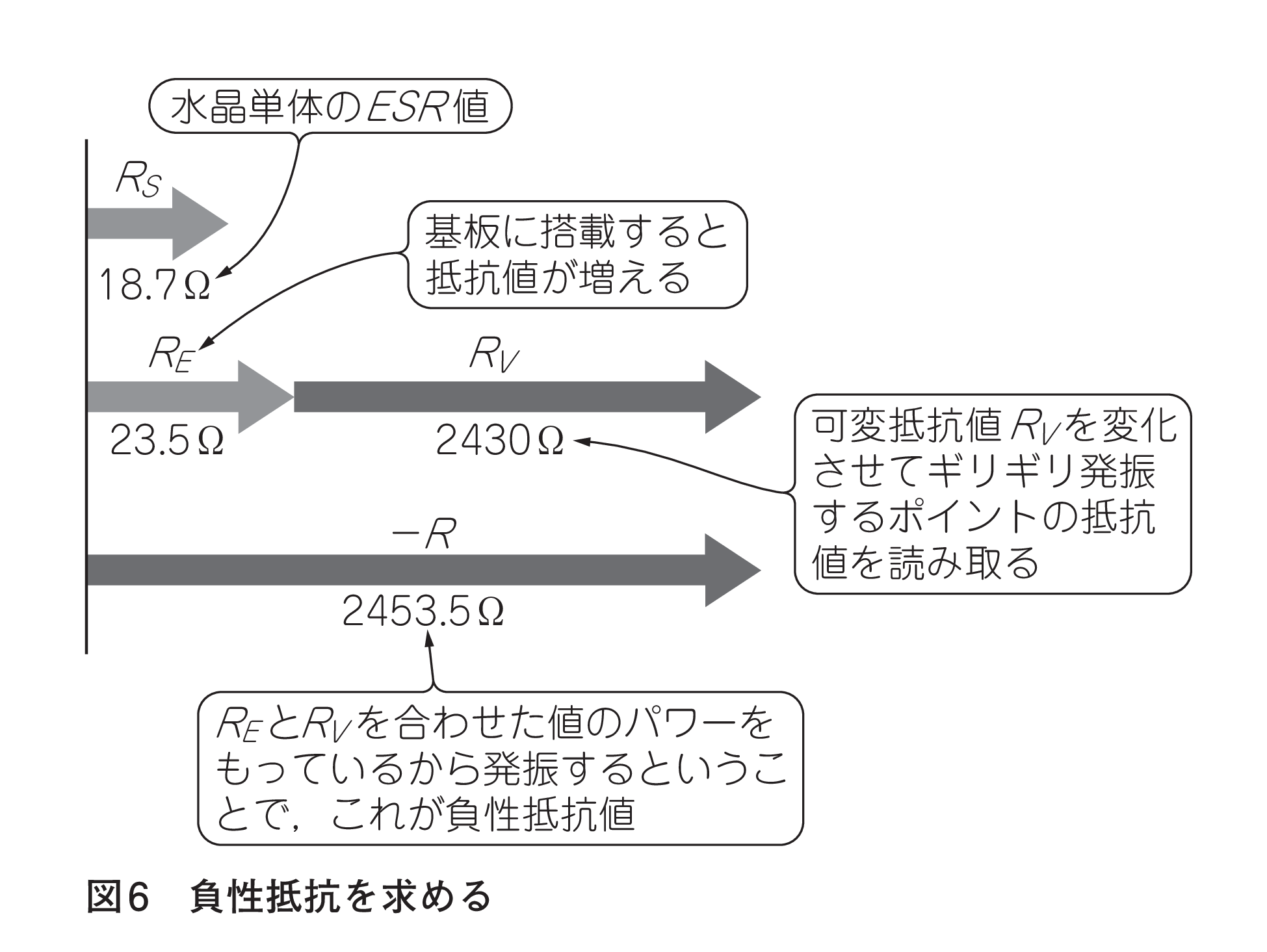

①搭載するサンプル水晶のESR 規格値を確認する

②規格値ぎりぎりの水晶を回路に入れたと想定して、そのときの抵抗値を式(2)で求める

このREの値は実測値ではなく、計算で算出された数値です。

③発振余裕度を式(1)で求める

この余裕度が5以上であれば、おおむね良しとの判断となります。

発振余裕度というのは規格ぎりぎりのESR値の水晶が搭載されたことを想定した、計算上の数値です(図7)。

● ドライブ・レベルを求める

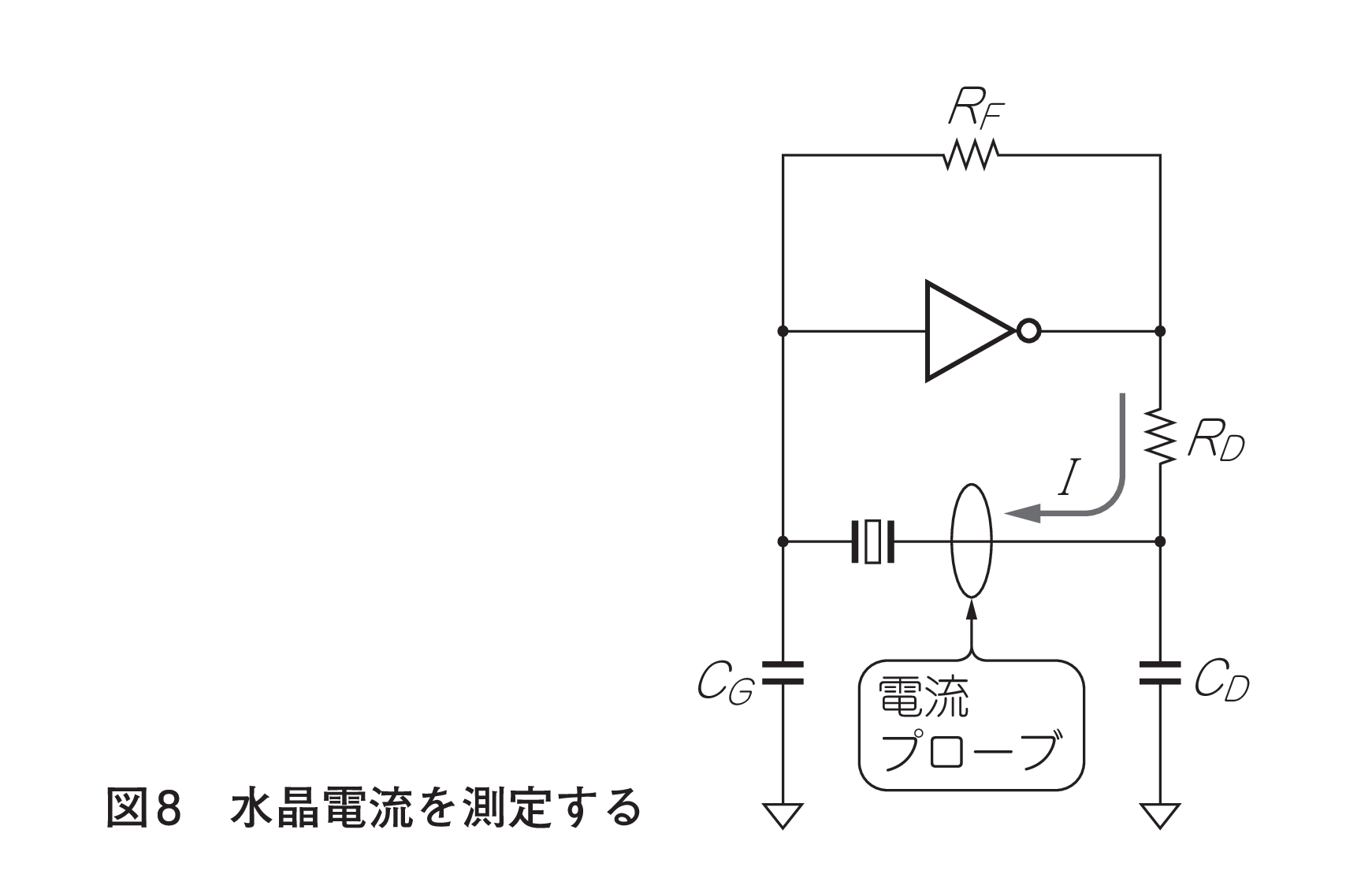

①図8のように電流プローブで水晶の電流値を測定する

②ドライブ・レベルLDを式(3)で計算する

ドライブ・レベルは通常100μWあたりが適切とされていますが、低ドライブ用のICの場合は数μWのこともあります。

● 周波数偏差を求める

ここで言う「周波数偏差」というのは、基板と水晶の基準のずれです。

入手したサンプル水晶単体の周波数偏差とは異なります。

回路マッチングにおける周波数偏差は次のようにして求めます。

①搭載した水晶単体の周波数fLを確認する(aとする)

②図8において電流プローブを水晶ホット端子に当てて、基板上の水晶の発振周波数を求める(bとする)

③周波数偏差Δfを式(5)で求める(公称周波数をf0とする)

この値がなるべく0ppmに近いほうが良いということです。

基板と水晶の基準のずれがゼロに近いということだからです。

ずれがあっても機能面で問題なければ、ユーザ判断でそのままで量産に入ってもかまいません。

※さらに詳しい内容は、こちらの書籍に掲載されております。

[特集] fsの超低ジッタと高周波化を実現するPLLの作り方

5G時代の低ジッタ GHzシンセサイザ設計基礎

トランジスタ技術編集部 / 編

定価880円(税込)

https://shop.cqpub.co.jp/detail/2512/