Vol.6 技術情報

水晶発振回路の回路マッチングとは⑤【回路マッチングで行うこと】

回路マッチングで行うこと

回路マッチングではまず受領した現状での状況を確認し、改善すべき項目があったら個別/具体的に調整していきます。

● はじめに負性抵抗の極大化のため回路上の外付けコンデンサやダンピング抵抗の値を調整する

回路マッチングで最初に行うのは「負性抵抗の極大化」です。

ICは水晶を駆動させる一定のパワーをもっていますが、そのパワーは回路上の外付けコンデンサ(C)やダンピング抵抗(RD)の値を変化させることで調整ができます。

CやRDの値を変えることによってICのパワー、すなわち負性抵抗(-R)が最大になるようにする、これが回路マッチングの第一の目標です。

● 次に発振余裕度を算出、これが5倍以上になるようにする

発振余裕度は、式(1)で与えられます。

-R:負性抵抗[Ω]

RE:負荷時等価抵抗[Ω]

RE(負荷時等価抵抗)は水晶を実際に基板に搭載したときの抵抗値のことですが、

この値は水晶単体の抵抗値ESR(RS)とは異なります。

REは式(2)で与えられます。

RS:ESRの規格値[Ω]

CL:負荷容量[F]

C0:並列容量[F]

水晶業界では一般に、この発振余裕度を5倍以上確保するように勧めています。

「ICのパワーが水晶の抵抗成分の5倍以上あること」ということです。

この5倍というのは経験則上導かれた数値であって、理論的に算出したものではありません。

● ドライブ・レベルを計算する

発振余裕度を確認したら、次は水晶に印加する電力(ドライブ・レベル LD)を計算します。

水晶を流れる電流値Iを算出し、先に求めたRE(負荷時等価抵抗)とともに式(3)で計算します。

● 「周波数偏差」の割り出し

最後に、周波数偏差(基板と水晶の基準のずれ)を割り出します。

水晶単体の周波数偏差と、その水晶を実際に基板に搭載したときの発振周波数を測定/算出して、その誤差を計算して周波数偏差を算出します。

この計算は複雑ですので、次章で説明します。

※さらに詳しい内容は、こちらの書籍に掲載されております。

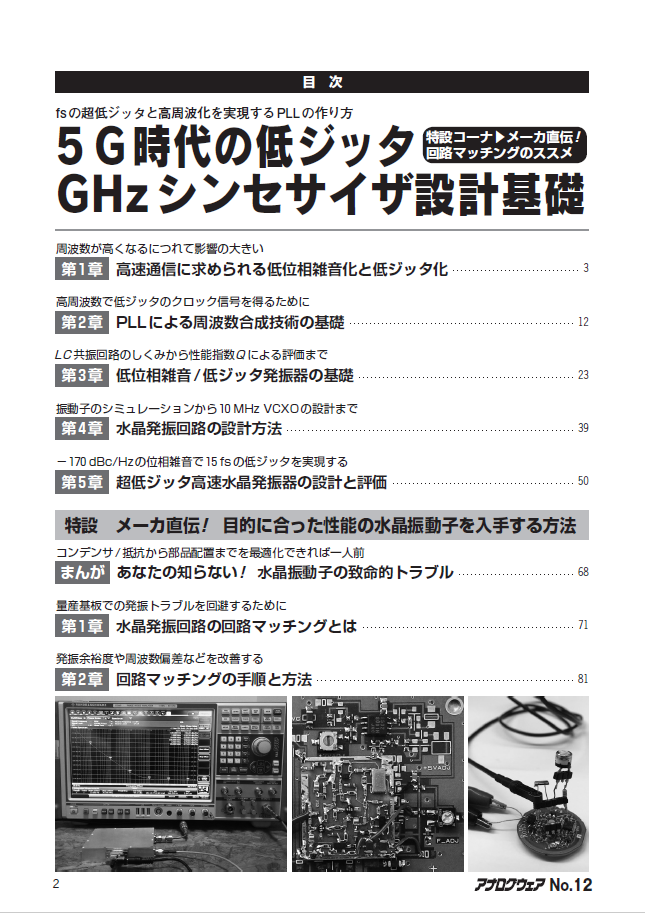

[特集] fsの超低ジッタと高周波化を実現するPLLの作り方

5G時代の低ジッタ GHzシンセサイザ設計基礎

トランジスタ技術編集部 / 編

定価880円(税込)

https://shop.cqpub.co.jp/detail/2512/